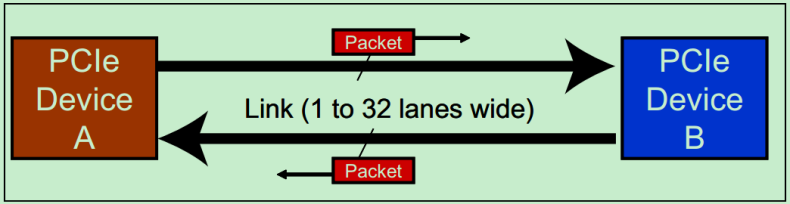

高速传输的时候,并行的连线直接干扰异常严重,而且随着频率的提高,干扰(EMI)越来越不可跨越。PCIe总线的提出可以算是代表着传统并行总线向高速串行总线发展的时代的到来。 实际上,不仅是PCI总线到PCIe总线,高速串行总线取代传统并行总线是一个大的趋势。如ATA到SATA,SCSI到USB等…… PCIe和PCI最大的改变是由并行改为串行,(补充,PCIE的信号线也变了,如不再支持legacy的中断,一些信号线不一样等,物理层面其实变化较大,但是在链路层,事务模型上是和PCI统一的), 虽然PCIe是一种串行总线,无法在物理层上兼容PCI总线,但是在软件层上面却是兼容PCI总线的。 和很多的串行总线一样,PCIe采用了全双工的传输设计,(PCI原来基本是半双工的,地址/数据线太多,不得不复用线路),即允许在同一时刻,同时进行发送和接收数据。 如下图所示,设备A和设备B之间通过双向的Link相连接,每个Link支持1到32个通道(Lane)。由于是串行总线,因此所有的数据(包括配置信息等)都是以数据包为单位进行发送的。

PCIe总线差异

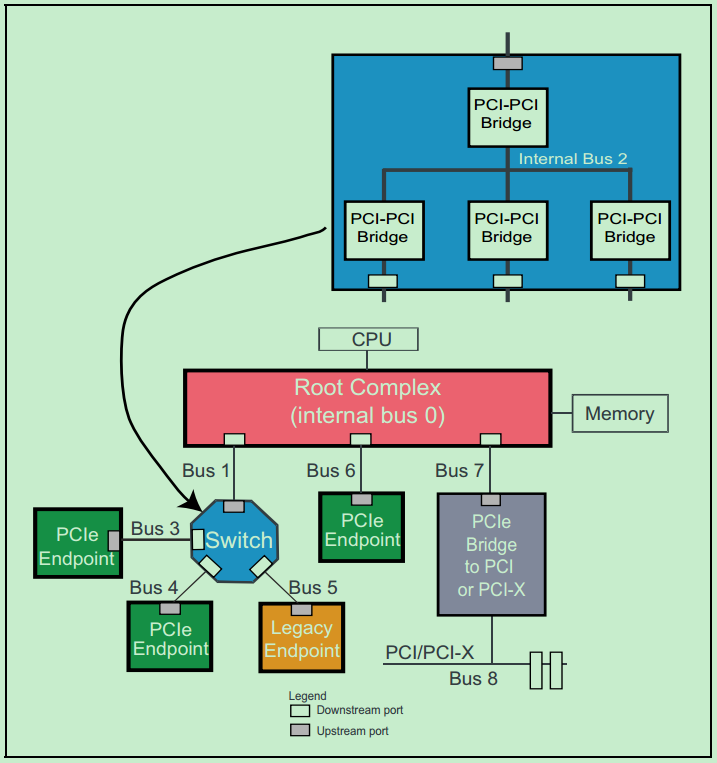

PCI是总线结构,而PCIe是点对点结构。 典型的结构是一个root port和一个endpoint直接组成一个点对点连接对,而Switch可以同时连接几个endpoint。一个root port和一个endpoint对就需要一个单独的PCI bus。 而PCI是在同一个总线上的设备共享同一个bus number。过去主板上的PCI插槽都公用一个PCI bus,而现在的PCIe插槽却连在芯片组不同的root port上。

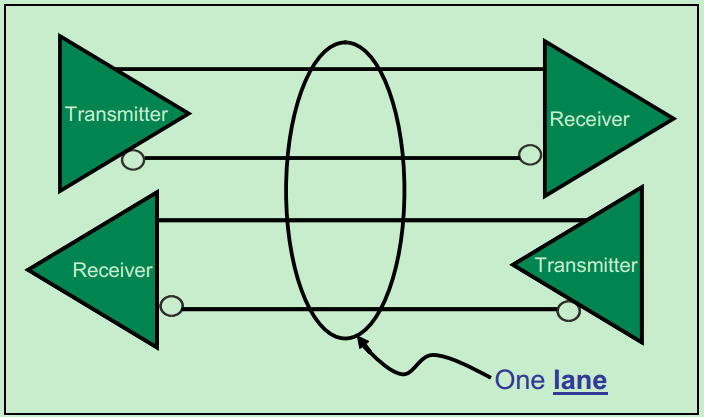

PCIe的连线是由不同的lane来连接的,这些lane可以合在一起提供更高的带宽。譬如两个1lane可以合成2lane的连接,写作x2。两个x2可以变成x4,最大直到x16,往往给带宽需求最大的显卡使用。

PCI配置空间从256B扩展为4k,同时提供了PCIe memory map访问方式

PCIe提供了很多特殊功能,如Complete Timeout(CTO),MaxPayload等等几十个特性,而且还在随着PCIe版本的进化不断增加中,对电源管理也提出了单独的State(L0/L0s/L1等等)

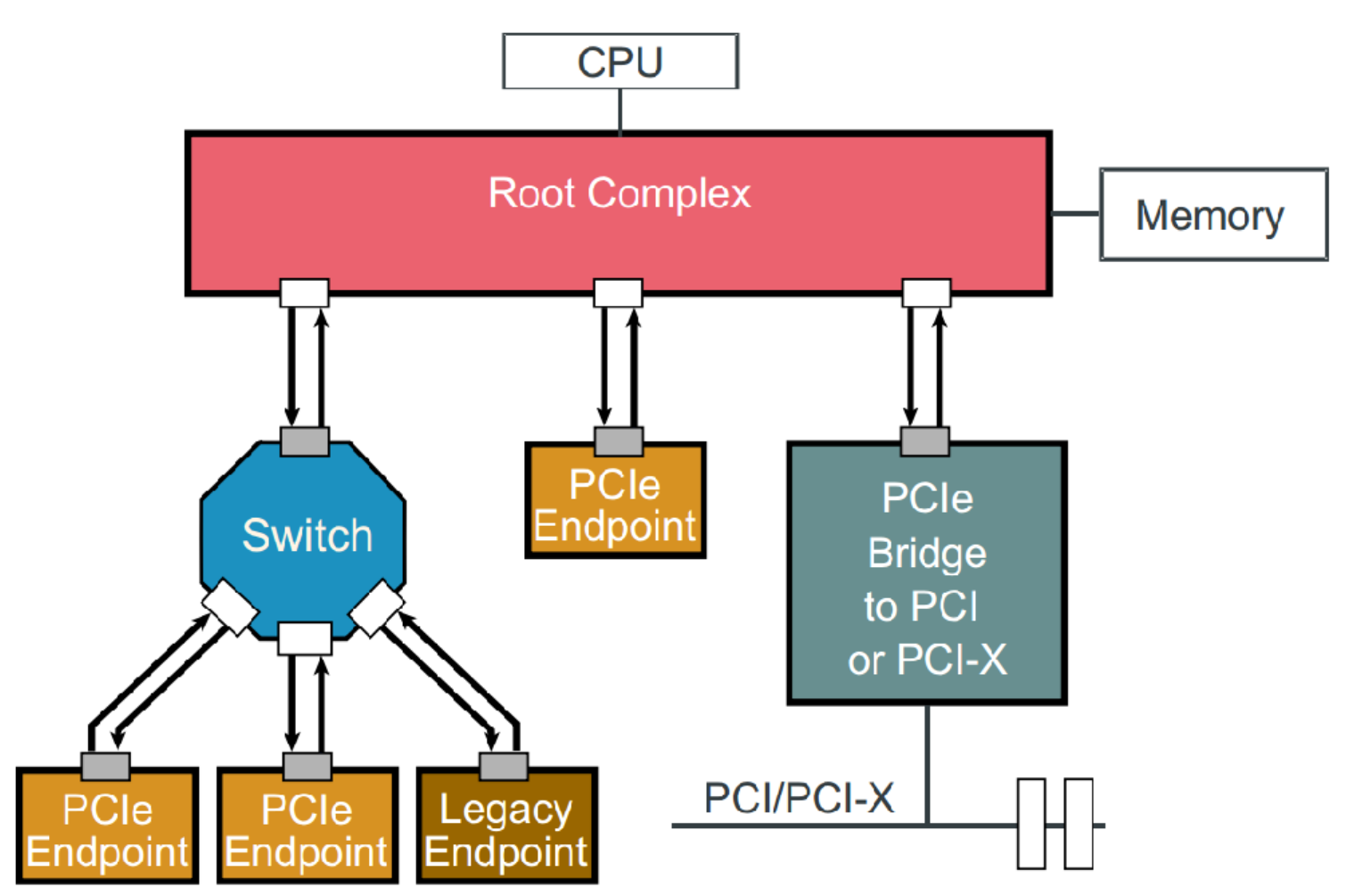

- Root Complex

- CPU和PCIe总线之间的接口可能会包含几个模块(处理器接口、DRAM接口等),甚至可能还会包含芯片,这个集合就称为Root Complex(根复合体), 它作为PCIe架构的根,代表CPU与系统其它部分进行交互。广义来说,Root Complex可以认为是CPU和PCIe拓扑之间的接口, Root Complex会将CPU的request转换成PCIe的4种不同的请求(Configuration、Memory、I/O、Message);

- Switch

- 从图中可以看出,Swtich提供扇出能力,让更多的PCIe设备连接在PCIe端口上;

- Bridge

- 桥接设备,用于去连接其他的总线,比如PCI总线或PCI-X总线,甚至另外的PCIe总线;

- PCIe Endpoint

- PCIe设备;

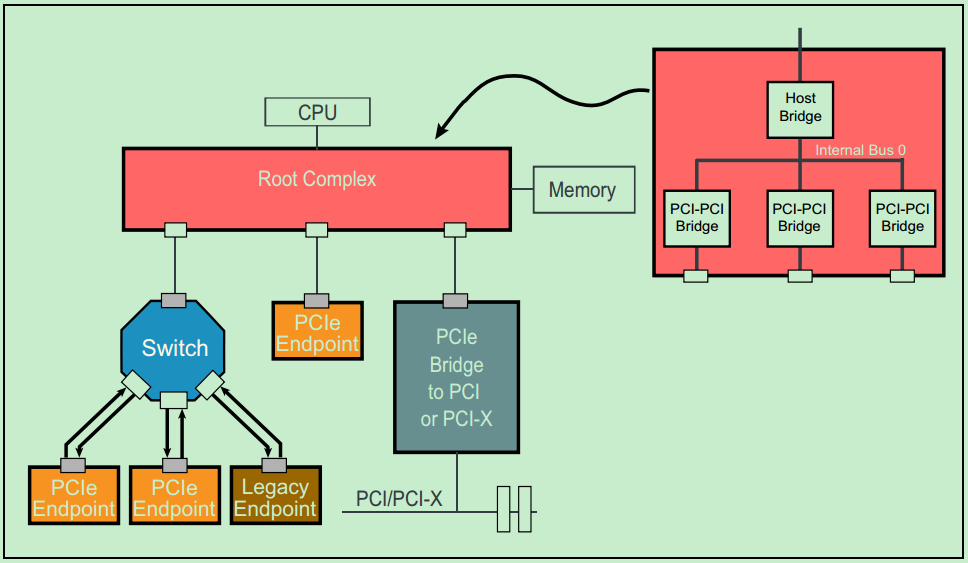

PCIe在软件上保持了后向兼容性,那么在PCIe的设计上,需要考虑在PCI总线上的软件视角,(逻辑结构)如Root Complex的实现可能就如下所示, 从而看起来与PCI总线相差无异。需要特别说明的是,Root Complex(RC or Root)和Switch都是全新的PCIe中的概念, 它们结构中的每一个端口(Port)都可以对应于PCI总线中的PCI-to-PCI桥的概念。也就是说,每一个RC和Switch中一般都有多个类似于PCI-to-PCI桥的东西。分别如下两张图所示

Root Complex通常会实现一个内部总线结构和多个桥,从而扇出到多个端口上; Root Complex的内部实现不需要遵循标准,因此都是厂家specific的;

Switch就是一个扩展设备,所以看起来像是各种桥的连接路由;