在PC时代,随着处理器的发展,经历了几代I/O总线的发展,解决的问题都是CPU主频提升与外部设备访问速度的问题: 第一代总线包含ISA、EISA、VESA和Micro Channel等; 第二代总线包含PCI、AGP、PCI-X等; 第三代总线包含PCIe、mPCIe、m.2等 PCIe(PCI Express)是目前PC和嵌入式系统中最常用的高速总线,PCIe在PCI的基础上发展而来,在软件上PCIe与PCI是后向兼容的,PCI的系统软件可以用在PCIe系统中。

PCI总线组成

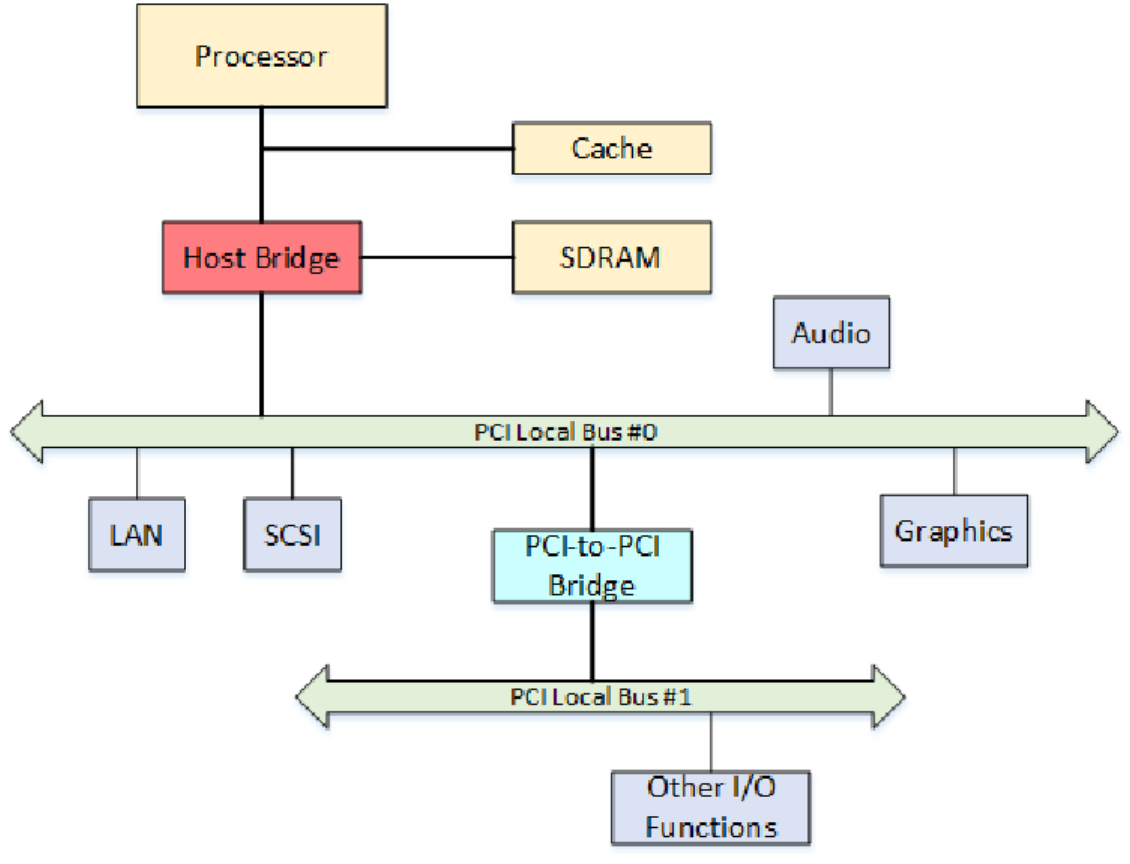

PCI 总线主要被分成三部分:PCI 设备,PCI 总线,PCI 桥。

- PCI总线

- 由Host Bridge或者PCI-to-PCI Bridge管理,用来连接各类设备,比如声卡、网卡、IDE接口等。 可以通过PCI-to-PCI Bridge来扩展PCI总线,并构成多级总线的总线树, 比如图中的PCI Local Bus #0和PCI Local Bus #1两条PCI总线就构成一颗总线树,同属一个总线域;

- PCI桥

- 用于扩展PCI总线,使采用PCI总线进行大规模系统互联成为可能,管理下游总线,并转发上下游总线之间的事务;

- PCI 设备

- PCI总线中有三类设备:PCI从设备,PCI主设备,桥设备。 PCI从设备:被动接收来自Host Bridge或者其他PCI设备的读写请求; PCI主设备:可以通过总线仲裁获得PCI总线的使用权,主动向其他PCI设备或主存储器发起读写请求; 桥设备:管理下游的PCI总线,并转发上下游总线之间的总线事务,包括PCI桥、PCI-to-ISA桥、PCI-to-Cardbus桥等。

- Host Bridge

- (如之前属于北桥芯片管理,现在已集成到x86 CPU中)管理PCI总线域,隔离处理器系统的存储器域与PCI总线域,并完成处理器与PCI设备间的数据交换, 包含处理器访问PCI设备的地址空间和PCI设备使用DMA机制访问主存储器,还可选的支持仲裁机制,热插拔等。 每个Host Bridge单独管理独立的总线空间,包括PCI Bus, PCI I/O, PCI Memory, and PCI Prefetchable Memory Space。

PCI总线信号定义

PCI总线是并行总线,而PCIE是串行总线。

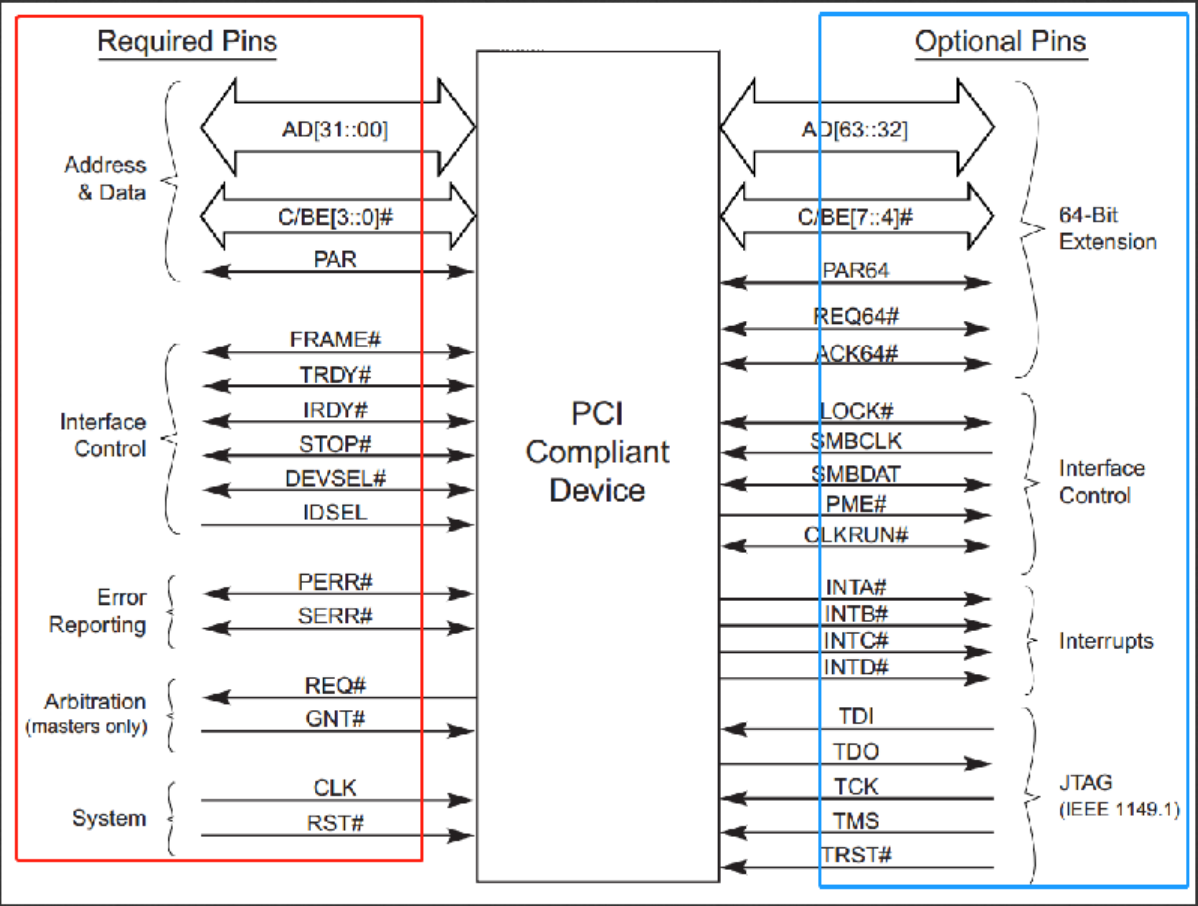

PCI信号大致解释:左侧红色框里表示的是PCI总线必需的信号,而右侧蓝色框里表示的是可选的信号;

- AD[31:00]:地址与数据信号复用,在传送时第一个时钟周期传送地址,下一个时钟周期传送数据;

- C/BE[3:0]#:PCI总线命令与字节使能信号复用,在地址周期中表示的是PCI总线命令,在数据周期中用于字节选择,可以进行单字节、字、双字访问;

- PAR:奇偶校验信号,确保AD[31:00]和C/BE[3:0]#传递的正确性;

- Interface Control:接口控制信号,主要作用是保证数据的正常传递,并根据PCI主从设备的状态,暂停、终止或者正常完成总线事务:

- FRAME#:表示PCI总线事务的开始与结束;

- IRDY#:信号由PCI主设备驱动,信号有效时表示PCI主设备数据已经ready;

- TRDY#:信号由目标设备驱动,信号有效时表示目标设备数据已经ready;

- STOP#:目标设备请求主设备停止当前总线事务;

- DEVSEL#:PCI总线的目标设备已经准备好;

- IDSEL:PCI总线在配置读写总线事务时,使用该信号选择PCI目标设备;

- Arbitration:仲裁信号,由REQ#和GNT#组成,与PCI总线的仲裁器直接相连,只有PCI主设备需要使用该组信号,每条PCI总线上都有一个总线仲裁器;

- Error Reporting:错误信号,包括PERR#奇偶校验错误和SERR系统错误;

- System:系统信号,包括时钟信号和复位信号;

PCI传输模式

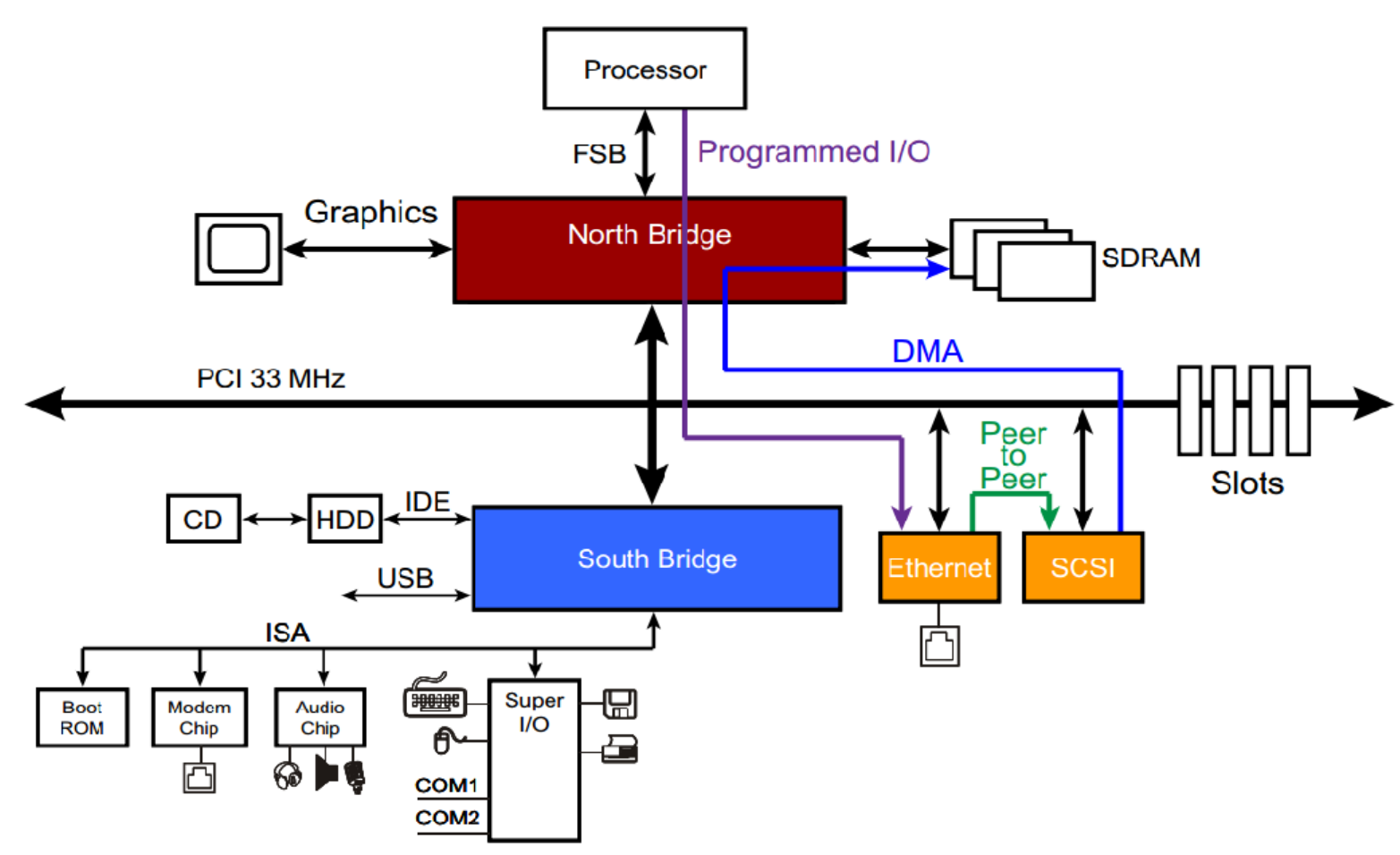

PCI使用三种模型用于数据的传输:

- Programmed I/O

- 通过IO读写访问PCI设备空间;PIO在早期的PC中被广泛使用,因外当时的处理器的速度要远远大于任何其他外设的速度,所以PIO足以胜任所有的任务。 举一个例子,比如说某一个PCI设备需要向内存(SDRAM)中写入一些数据,该PCI设备会向CPU请求一个中断,然后CPU首先先通过PCI总线把该PCI设备的数据读取到CPU内部的寄存器中, 然后再把数据从内部寄存器写入到内存(SDRAM)中。PIO已经逐渐被DMA传输方式所取代,但是为了兼容早期的一些设备,PCI Spec依然保留了PIO。

- DMA

- PIO的方式比较低效,DMA的方式可以直接去访问主存储器而无需CPU干预,效率更高;目前,几乎所有的CPU,甚至是MCU都支持DMA。

- Peer-to-peer

- 两台PCI设备之间直接传送数据;PCI总线系统中的主机身份并不是固定不变的,而是可以切换的(借助仲裁器),但是同一时刻只能存在一个主机。 完成Peer-to-Peer这一传输方式的前提是,PCI总线系统中至少存在一个有能力成为主机的设备。在仲裁器的控制下,完成主机身份的切换,进而获得PCI总线的控制权, 然后与总线上的其他PCI设备进行通信。不过,需要注意的是,在实际的系统中,Peer-to-Peer这一传输方式却很少被使用, 这是因为获得主机身份的PCI设备(Initiator)和另一个PCI设备(Target)通常采用不同的数据格式,除非他们是同一个厂家的设备。

PCI总线地址空间

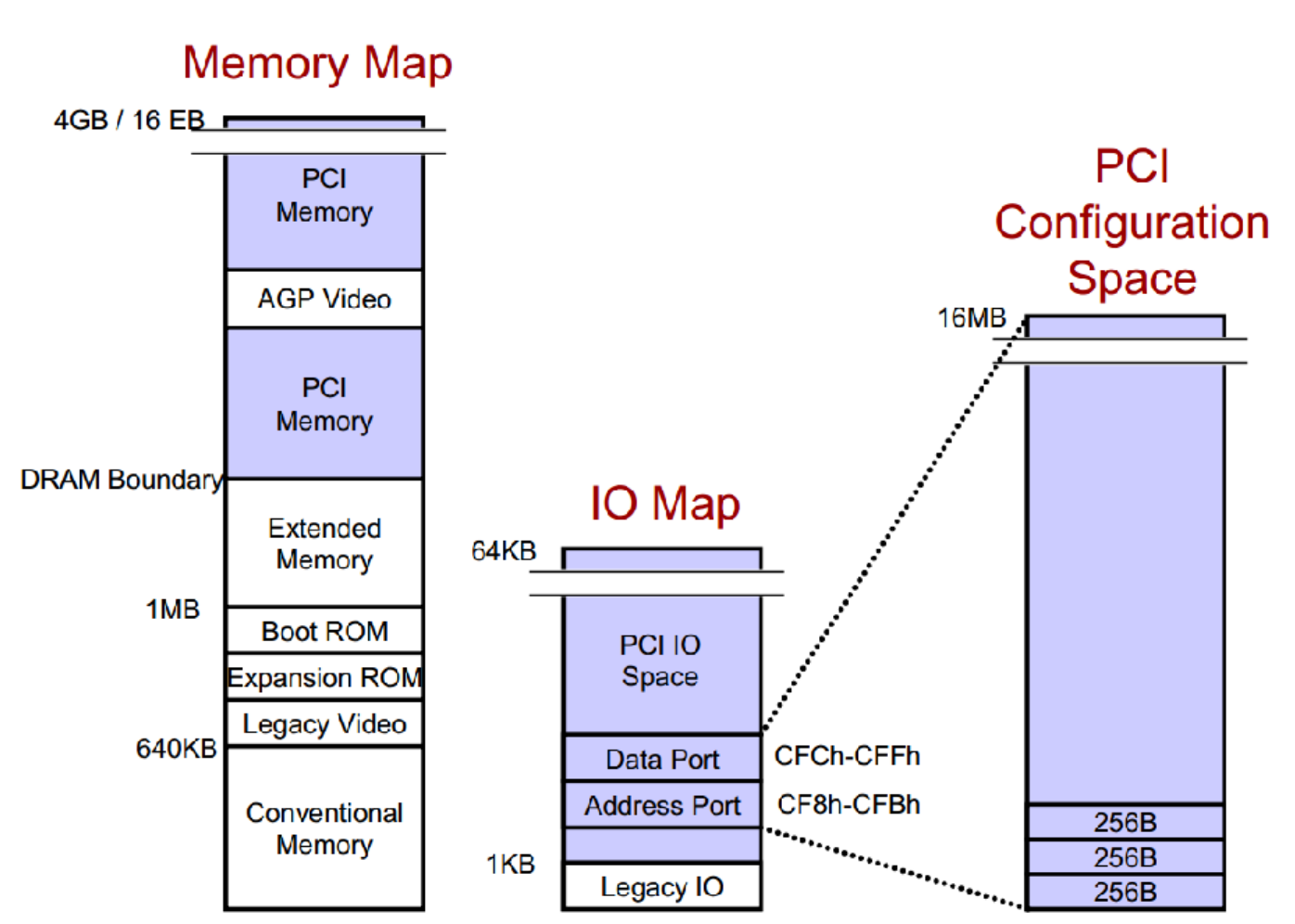

PCI体系架构支持三种地址空间:

memory空间:针对32bit寻址,支持4G的地址空间,针对64bit寻址,支持16EB的地址空间;

I/O空间 : PCI最大支持4G的IO空间,但受限于x86处理器的IO空间(16bits带宽),很多平台将PCI的IO地址空间限定在64KB;

配置空间 (私有空间) : x86 CPU可以直接访问memory空间和I/O空间,而配置空间则不能直接访问; 不同的芯片厂商访问配置空间的方法略有不同,以Intel的芯片组为例,其使用IO空间的CF8h/CFCh地址来访问PCI设备的配置寄存器:

每个PCI功能最多可以有256字节的配置空间;(这里特指PCI设备,非PCIe设备,PCIe设备兼容扩展PCI设备) PCI总线在进行配置的时候,采用ID译码方式,使用设备的ID号,包括Bus Number,Device Number,Function Number和Register Number, 每个系统支持256条总线,每条总线支持32个设备,每个设备支持8个功能,由于每个功能最多有256字节的配置空间,因此总的配置空间大小为:256B * 8 * 32 * 256 = 16M;

x86 CPU 访问配置空间

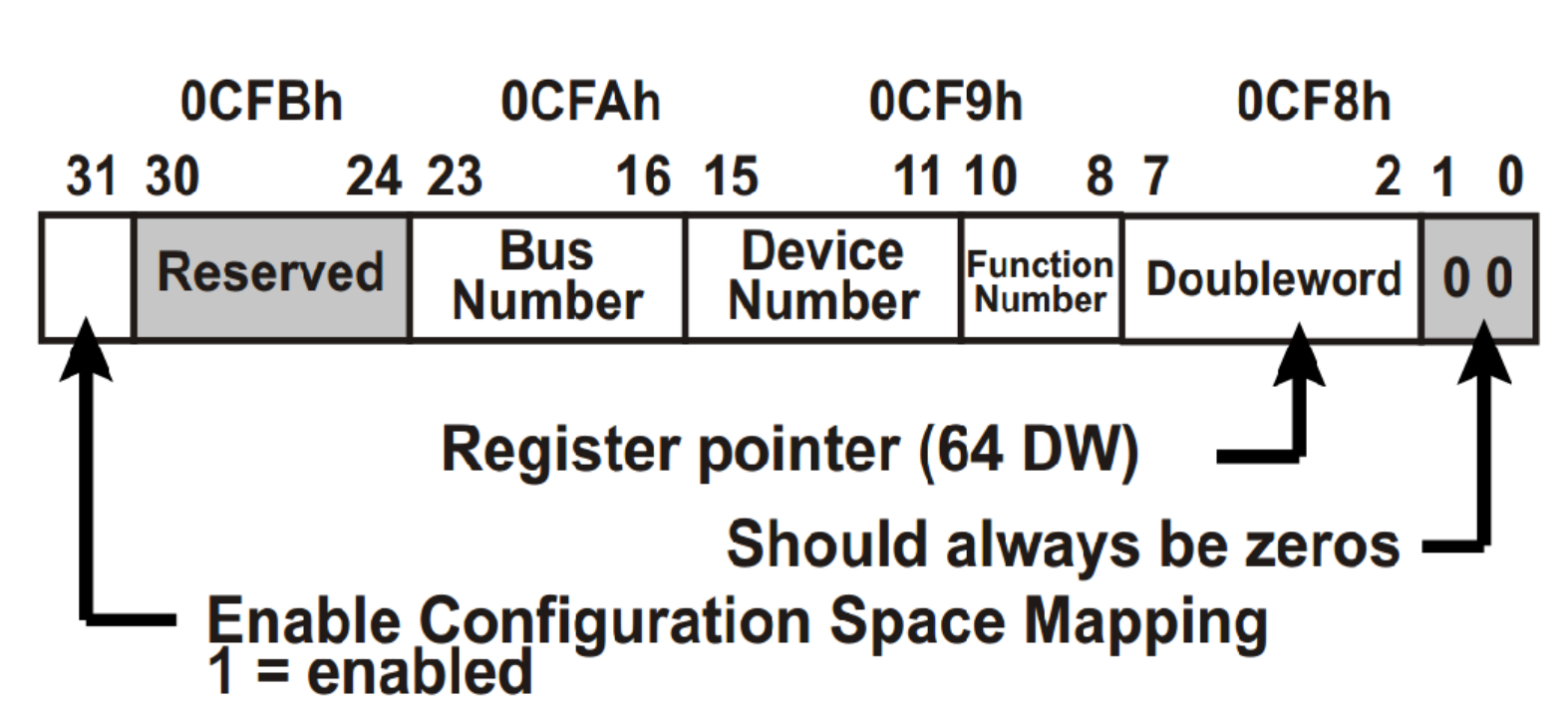

未规范PCI配置空间的访问方式,不同的CPU访问配置空间方式可能不同。在x86 CPU上, 通过IO映射的数据端口和地址端口间接访问PCI的配置空间,其中地址端口映射到0CF8h - 0CFBh,数据端口映射到0CFCh - 0CFFh;

PCI的配置过程分为两步:

- CPU写CF8h端口,其中写的内容如图所示,BUS,Device,Function能标识出特定的设备功能,Doubleword来指定配置空间的具体某个寄存器;

- CPU可以IO读写CFCh端口,用于读取步骤1中的指定寄存器内容,或者写入指定寄存器内容。 这个过程有点类似于通过I2C去配置外接芯片;

注:在PCIe中,则引入了一种新的Configuration Address Space访问方式:将其直接映射到了Memory Address Space当中。 PCIe规范在PCI规范的基础上,将配置空间扩展到4KB。原来的CF8/CFC方法仍然可以访问所有PCIe设备配置空间的头255B。剩下的配置空间 在Intel CPU上被映射到MMIO(Memory Map IO),就像内存一样访问。MMIO的起始位置,具体位置可以由平台进行设置,设置寄存器一般在Root complex中。

绝大多数PCI设备将PCI配置信息存放在E2PROM中,PCI设备进行上电初始化,将E2PROM中的信息读到PCI设备的配置空间中作为初始值,这个操作由硬件完成。

PCI地址空间隔离/转换

PCI设备具有独立的地址空间,即PCI总线地址空间。PCI地址空间与处理器地址空间隔离。该空间与存储器地址空间通过Host bridge隔离。 处理器需要通过Host bridge才能访问PCI设备,而PCI设备需要通过Host bridge才能主存储器。在Host bridge中含有许多缓冲, 这些缓冲使得处理器总线与PCI总线工作在各自的时钟频率中,彼此互不干扰。Host bridge的存在也使得PCI设备和处理器可以方便地共享主存储器资源。 处理器访问PCI设备时,必须通过Host bridge进行地址转换;而PCI设备访问主存储器时,也需要通过Host bridge进行地址转换。(这里有一级抽象)

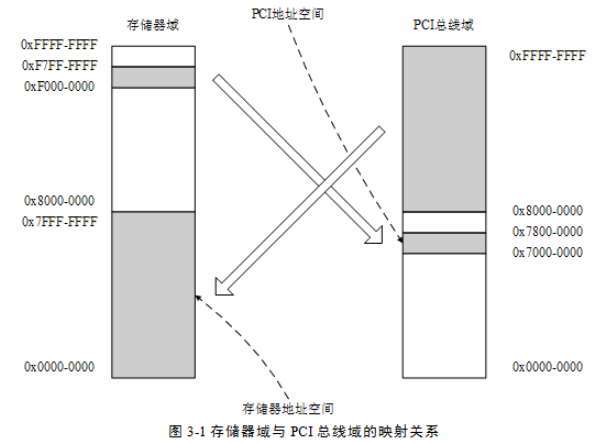

我们假设在一个32位处理器中,其存储器域的0xF000-0000~0xF7FF-FFFF(共128MB)这段物理地址空间与PCI总线的地址空间存在映射关系。 当处理器访问这段存储器地址空间时,HOST主桥将会认领这个存储器访问,并将这个存储器访问使用的物理地址空间转换为PCI总线地址空间,并与0x7000-0000~0x77FF-FFFF这段PCI总线地址空间对应。 为简化起见,我们假定在存储器域中只映射了PCI设备的存储器地址空间,而不映射PCI设备的I/O地址空间。而PCI设备的BAR空间使用0x7000-0000~0x77FF-FFFF这段PCI总线域的存储器地址空间。

当PCI设备使用DMA机制,访问存储器域地址空间时,处理器系统同样需要将存储器域的地址空间反向映射到PCI总线地址空间。假设在一个处理器系统中, 如果主存储器大小为2GB,其在存储器域的地址范围为0x0000-0000~0x7FFF-FFFF,而这段地址在PCI总线域中对应的“PCI总线地址空间”为0x8000-0000~0xFFFF-FFFF。

因此PCI设备进行DMA操作时,必须使用0x8000-0000~0xFFFF-FFFF这段PCI总线域的地址,HOST主桥才能认领这个PCI总线事务, 并将这个总线事务使用的PCI总线地址转换为存储器地址,并与0x0000-0000~0x7FFF-FFFF这段存储器区域进行数据传递。

在一个实际的处理器系统中,很少有系统软件采用这样的方法,实现存储器域与PCI总线域之间的映射,“简单相等”还是最常用的映射方法。 在x86处理器的HOST主桥中,存储器域的存储器地址与PCI总线地址相等,这种“简单相等”也是一种映射关系。